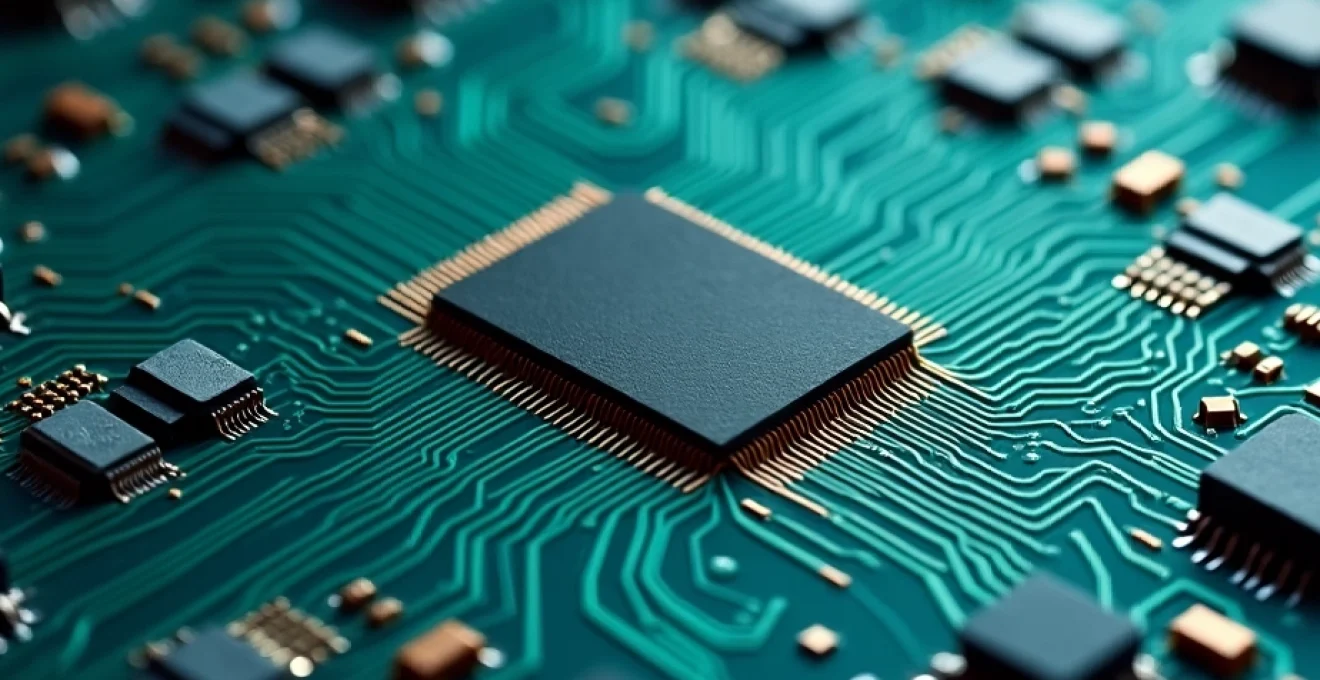

Die Herstellung von Leiterplatten ist ein faszinierender und komplexer Prozess, der die Grundlage für nahezu alle elektronischen Geräte bildet. Von Smartphones über Laptops bis hin zu industriellen Steuerungssystemen – überall finden sich diese technologischen Meisterwerke. Der moderne Fertigungsprozess einer Leiterplatte vereint präzise Ingenieurskunst mit hochentwickelten Fertigungstechniken, um miniaturisierte elektronische Schaltungen zu realisieren.

Designphase und CAD-Erstellung für Leiterplatten

Der Fertigungsprozess einer Leiterplatte beginnt lange bevor die erste Maschine in Betrieb genommen wird. Alles startet mit der sorgfältigen Planung und dem Design der Schaltung. Ingenieure nutzen spezialisierte CAD-Software (Computer-Aided Design), um die komplexen Schaltpläne zu entwerfen und in ein Layout zu überführen, das später auf die Leiterplatte übertragen wird.

In dieser Phase werden kritische Entscheidungen getroffen, die die Leistung, Zuverlässigkeit und Herstellbarkeit der Leiterplatte massgeblich beeinflussen. Die Platzierung der Komponenten, die Breite und der Verlauf der Leiterbahnen sowie die Anzahl der Lagen bei Multilayer-Platinen werden hier festgelegt. Moderne CAD-Tools bieten fortschrittliche Funktionen wie automatisches Routing und Design Rule Checking , um potenzielle Fehler frühzeitig zu erkennen und zu beheben.

Eine besondere Herausforderung stellt die Optimierung des Designs für die elektromagnetische Verträglichkeit (EMV) dar. Hier müssen Ingenieure sicherstellen, dass die Leiterplatte weder durch externe Störquellen beeinträchtigt wird noch selbst unzulässige elektromagnetische Emissionen verursacht. Dies erfordert oft mehrere Iterationen und Simulationen, bevor das finale Design freigegeben wird.

Materialbeschaffung und Substratvorbereitung

Nachdem das Design finalisiert wurde, beginnt die eigentliche Fertigung mit der Auswahl und Vorbereitung des Basismaterials. Die Wahl des richtigen Substrats ist entscheidend für die Leistungsfähigkeit und Langlebigkeit der Leiterplatte. Häufig verwendet wird FR-4, ein glasfaserverstärktes Epoxidharz-Laminat, das sich durch gute elektrische Isolationseigenschaften und mechanische Stabilität auszeichnet.

Die Substratvorbereitung umfasst mehrere Schritte:

- Zuschneiden des Rohmaterials auf die gewünschte Grösse

- Reinigung der Oberfläche von Verunreinigungen

- Aufbringen einer dünnen Kupferschicht (bei nicht vorkupierten Platten)

- Vorbehandlung der Oberfläche für bessere Haftung des Photoresists

Bei Multilayer-Leiterplatten werden in dieser Phase auch die einzelnen Lagen vorbereitet und mit sogenannten Prepreg-Schichten (vorimprägnierte Glasfasermatten) zu einem Stapel angeordnet. Dieser Stapel wird später unter Hitze und Druck zu einer einzigen Einheit verpresst.

Die Qualität des Substrats und die Präzision der Vorbereitung haben direkten Einfluss auf die spätere Funktionalität der Leiterplatte. Selbst kleinste Verunreinigungen oder Unebenheiten können zu Fehlern in den nachfolgenden Prozessschritten führen. Daher wird in modernen Fertigungsanlagen grösster Wert auf Reinraumtechnik und strenge Qualitätskontrollen gelegt.

Fotolithografischer Prozess und Ätztechniken

Der fotolithografische Prozess ist das Herzstück der leiterplatte manufacturingprozess. Hier wird das Design der Leiterplatte tatsächlich auf das Substrat übertragen. Dieser Vorgang erfordert höchste Präzision und modernste Technologie, um die immer feiner werdenden Strukturen auf den Leiterplatten realisieren zu können.

Belichtung mit Photoresist-Technologie

Der erste Schritt des fotolithografischen Prozesses ist das Aufbringen einer lichtempfindlichen Schicht, des sogenannten Photoresists, auf die Kupferoberfläche der Leiterplatte. Diese Schicht wird anschliessend durch eine Maske belichtet, die das negative Bild der gewünschten Leiterbahnstrukturen enthält. UV-Licht härtet die belichteten Bereiche des Photoresists aus, während die unbelichteten Bereiche löslich bleiben.

Moderne Fertigungsanlagen setzen zunehmend auf Direct Imaging -Systeme, die das Design direkt aus den CAD-Daten auf den Photoresist projizieren. Dies erhöht die Präzision und ermöglicht schnellere Anpassungen bei Designänderungen.

Entwicklung und Strukturierung der Leiterbahnen

Nach der Belichtung folgt der Entwicklungsprozess. Hierbei wird die Leiterplatte in ein Entwicklerbad getaucht, das die nicht ausgehärteten Bereiche des Photoresists entfernt. Zurück bleibt ein exaktes Abbild der gewünschten Leiterbahnstruktur auf der Kupferoberfläche.

Die Präzision dieses Schrittes ist entscheidend für die Qualität der fertigen Leiterplatte. Selbst kleinste Abweichungen können zu Kurzschlüssen oder unterbrochenen Leiterbahnen führen. Daher kommen hier hochspezialisierte Entwicklungsanlagen zum Einsatz, die Parameter wie Temperatur, Entwicklerkonzentration und Einwirkzeit genau kontrollieren.

Nasschemisches Ätzen vs. Plasmaätzen

Nach der Entwicklung folgt der eigentliche Ätzprozess, bei dem das überschüssige Kupfer entfernt wird. Hier stehen zwei Hauptverfahren zur Verfügung: das nasschemische Ätzen und das Plasmaätzen.

Beim nasschemischen Ätzen wird die Leiterplatte in ein Ätzbad getaucht, typischerweise eine Lösung aus Eisen(III)-chlorid oder Ammoniumpersulfat. Diese Chemikalien lösen das ungeschützte Kupfer auf, während die vom Photoresist bedeckten Bereiche intakt bleiben.

Das nasschemische Ätzen ist zwar kostengünstig und für viele Anwendungen ausreichend, stösst jedoch bei extrem feinen Strukturen an seine Grenzen.

Für hochpräzise Leiterplatten mit besonders feinen Strukturen kommt zunehmend das Plasmaätzen zum Einsatz. Hierbei wird das Kupfer durch ein reaktives Plasma abgetragen. Dieses Verfahren ermöglicht eine bessere Kontrolle über den Ätzprozess und kann feinere Strukturen realisieren, ist jedoch auch kostenintensiver.

Qualitätskontrolle durch AOI-Systeme

Nach dem Ätzen durchlaufen die Leiterplatten eine rigorose Qualitätskontrolle. Hierbei kommen modernste Automated Optical Inspection (AOI) Systeme zum Einsatz. Diese hochauflösenden Kamerasysteme scannen die gesamte Oberfläche der Leiterplatte und vergleichen sie mit dem Soll-Layout aus den CAD-Daten.

AOI-Systeme können kleinste Abweichungen, Kurzschlüsse oder Unterbrechungen in den Leiterbahnen erkennen, die dem menschlichen Auge verborgen bleiben würden. Sie spielen eine entscheidende Rolle bei der Sicherstellung der Qualität und Zuverlässigkeit moderner Leiterplatten, insbesondere angesichts der zunehmenden Miniaturisierung und Komplexität elektronischer Schaltungen.

Lötstopplack-Auftrag und Oberflächenbehandlung

Nach dem erfolgreichen Ätzen der Leiterbahnen folgt der Auftrag des Lötstopplacks. Dieser Schritt ist entscheidend für den Schutz der Leiterplatte und die Vorbereitung auf den späteren Lötprozess. Der Lötstopplack, oft in charakteristischem Grün oder anderen Farben, wird mittels Siebdruck oder modernerer Inkjet-Verfahren aufgebracht.

Die Funktionen des Lötstopplacks sind vielfältig:

- Schutz der Leiterbahnen vor Umwelteinflüssen und Korrosion

- Verhinderung von unbeabsichtigten Lötbrücken während des Lötprozesses

- Verbesserung der elektrischen Isolation zwischen den Leiterbahnen

- Erleichterung der visuellen Inspektion durch Kontrastbildung

Nach dem Auftrag des Lötstopplacks erfolgt eine Oberflächenbehandlung der freiliegenden Kupferflächen. Diese Behandlung ist essenziell für die spätere Lötbarkeit und den Schutz vor Oxidation. Gängige Verfahren sind:

- HASL (Hot Air Solder Leveling): Aufbringen einer dünnen Zinn-Blei-Schicht

- ENIG (Electroless Nickel Immersion Gold): Aufbringen einer Nickel- und Goldschicht

- OSP (Organic Solderability Preservative): Auftrag einer organischen Schutzschicht

- Immersion Silber oder Immersion Zinn: Chemische Abscheidung von Silber oder Zinn

Die Wahl der Oberflächenbehandlung hängt von verschiedenen Faktoren ab, einschliesslich der späteren Anwendung der Leiterplatte, der erforderlichen Lagerfähigkeit und der Kompatibilität mit den zu verwendenden Lötverfahren.

Bestückung und Lötprozesse

Mit der fertigen, oberflächenbehandelten Leiterplatte beginnt nun die Phase der Bestückung und des Lötens. Dieser Prozess transformiert die „nackte“ Leiterplatte in eine funktionsfähige elektronische Baugruppe. Die Komplexität dieses Schrittes hat in den letzten Jahrzehnten erheblich zugenommen, bedingt durch die Miniaturisierung der Bauteile und die Zunahme der Packungsdichte auf modernen Leiterplatten.

SMD-Bestückung mit Pick-and-Place-Maschinen

Die meisten modernen Leiterplatten werden hauptsächlich mit SMD-Bauteilen (Surface Mounted Devices) bestückt. Hierfür kommen hochpräzise Pick-and-Place-Maschinen zum Einsatz. Diese Automaten können tausende Bauteile pro Stunde mit einer Genauigkeit von wenigen Mikrometern platzieren.

Der Prozess läuft typischerweise wie folgt ab:

- Auftrag von Lotpaste auf die Lötpads mittels Schablonendruck

- Optische Erkennung der Bauteilposition und -ausrichtung

- Aufnehmen des Bauteils mit einem Vakuumgreifer

- Präzises Platzieren des Bauteils auf der Leiterplatte

- Optische Kontrolle der korrekten Positionierung

Die Effizienz und Präzision dieses Prozesses ist entscheidend für die Qualität und Zuverlässigkeit der fertigen elektronischen Baugruppe. Moderne Pick-and-Place-Maschinen sind in der Lage, selbst kleinste Bauteile wie 0201 oder 01005 Chips zuverlässig zu handhaben.

Reflow-Lötverfahren für SMD-Komponenten

Nach der Bestückung durchlaufen die Leiterplatten den Reflow-Lötprozess. Hierbei werden sie in einem speziellen Ofen einem präzise kontrollierten Temperaturprofil ausgesetzt. Die Lotpaste schmilzt, benetzt die Anschlüsse der Bauteile und der Leiterplatte und bildet beim Abkühlen eine feste, elektrisch leitfähige Verbindung.

Das Temperaturprofil beim Reflow-Löten ist kritisch und muss sorgfältig auf die verwendeten Bauteile und Materialien abgestimmt werden. Es umfasst typischerweise vier Phasen:

- Vorheizphase: Langsames Erwärmen zur Vermeidung von Thermoshocks

- Aktivierungsphase: Aktivierung der Flussmittel in der Lotpaste

- Reflowphase: Kurzzeitiges Überschreiten der Schmelztemperatur des Lotes

- Abkühlphase: Kontrolliertes Abkühlen zur Bildung stabiler Lötverbindungen

Die Präzision des Reflow-Lötprozesses ist entscheidend für die Qualität und Zuverlässigkeit der Lötverbindungen. Selbst kleine Abweichungen können zu kalten Lötstellen, Lötperlen oder anderen Defekten führen.

Wellenlöten für THT-Bauteile

Während SMD-Bauteile durch Reflow-Löten verbunden werden, erfordern durchsteckmontierte Bauteile (Through-Hole Technology, THT) einen anderen Ansatz. Hier kommt das Wellenlötverfahren zum Einsatz, das besonders für grössere Komponenten und Steckverbinder geeignet ist.

Der Wellenlötprozess umfasst typischerweise folgende Schritte:

- Fluxen: Auftragen eines Flussmittels zur Reinigung und Verbesserung der Benetzung

- Vorheizen: Erwärmung der Leiterplatte zur Reduzierung von Thermoshocks

- Wellenlöten: Kontakt der Unterseite der Leiterplatte mit einer stehenden Welle aus geschmolzenem Lot

- Abkühlen: Kontrollierte Abkühlung zur Bildung stabiler Lötverbindungen

Die Herausforderung beim Wellenlöten liegt in der präzisen Kontrolle der Lottemperatur und der Geschwindigkeit, mit der die Leiterplatte durch die Lötwelle geführt wird. Zu hohe Temperaturen oder zu lange Kontaktzeiten können zu Beschädigungen der Bauteile oder der Leiterplatte führen, während zu niedrige Temperaturen oder zu kurze Kontaktzeiten unvollständige Lötverbindungen zur Folge haben können.

Selektivlöten für gemischte Bestückungen

In modernen elektronischen Geräten finden sich oft Leiterplatten mit einer Mischung aus SMD- und THT-Bauteilen. Um beide Technologien effizient zu kombinieren, hat sich das Selektivlöten als präzise Methode etabliert. Dabei werden nur spezifische Bereiche der Leiterplatte gelötet, was besonders bei empfindlichen Komponenten von Vorteil ist.

Der Selektivlötprozess umfasst folgende Hauptschritte:

- Präzise Fluxapplikation auf die zu lötenden Stellen

- Punktuelles Vorheizen der Lötstellen

- Gezieltes Löten durch eine miniaturisierte Lötwelle oder einen Lötkolben

Selektivlöten ermöglicht eine hohe Flexibilität in der Produktion und reduziert die thermische Belastung der Leiterplatte. Es ist besonders nützlich für komplexe Baugruppen, bei denen verschiedene Komponenten unterschiedliche Lötparameter erfordern.

Die Kombination verschiedener Löttechniken in einem modernen Fertigungsprozess erfordert sorgfältige Planung und Abstimmung, um optimale Ergebnisse zu erzielen und die Qualität jeder einzelnen Lötverbindung zu gewährleisten.

Endkontrolle und Funktionstest der Leiterplatte

Nach Abschluss aller Fertigungs- und Lötprozesse durchläuft jede Leiterplatte eine umfassende Endkontrolle und Funktionstests. Diese Phase ist entscheidend, um die Qualität und Zuverlässigkeit des Endprodukts sicherzustellen. Moderne Prüfverfahren kombinieren visuelle, elektrische und funktionale Tests, um selbst kleinste Fehler zu erkennen.

Optische Inspektion

Die optische Inspektion ist oft der erste Schritt der Endkontrolle. Hierbei kommen fortschrittliche AOI-Systeme (Automated Optical Inspection) zum Einsatz, die jede Leiterplatte mit hochauflösenden Kameras scannen. Diese Systeme können:

- Fehlende oder falsch platzierte Bauteile erkennen

- Lötqualität beurteilen und Lötfehler wie Brücken oder kalte Lötstellen identifizieren

- Oberflächenbeschädigungen oder Verunreinigungen detektieren

Für besonders kritische oder komplexe Baugruppen wird zusätzlich oft eine Röntgeninspektion durchgeführt. Diese ermöglicht es, verdeckte Lötverbindungen, wie sie bei BGA-Chips (Ball Grid Array) vorkommen, zu überprüfen.

Elektrische Tests

Nach der optischen Kontrolle folgen elektrische Tests, um die Funktionalität der Schaltung zu verifizieren. Zwei Hauptmethoden kommen hier zum Einsatz:

- In-Circuit-Test (ICT): Hierbei wird die Leiterplatte mit einem speziellen Testadapter kontaktiert, der alle relevanten Messpunkte gleichzeitig erreicht. Der ICT prüft einzelne Komponenten und Verbindungen auf korrekte Werte und Funktionalität.

- Flying Probe Test: Bei diesem flexibleren Verfahren tasten bewegliche Prüfspitzen sequenziell verschiedene Testpunkte auf der Leiterplatte ab. Es ist besonders für Kleinserien oder Prototypen geeignet, da keine speziellen Testadapter erforderlich sind.

Funktionale Tests

Der abschliessende Schritt ist oft ein umfassender Funktionstest, bei dem die Leiterplatte unter realen Betriebsbedingungen getestet wird. Hierbei werden:

- Alle Funktionen der Schaltung überprüft

- Leistungsparameter gemessen und mit Sollwerten verglichen

- Stresstest durchgeführt, um die Zuverlässigkeit unter extremen Bedingungen zu testen

Für komplexe Systeme können diese Tests mehrere Stunden dauern und verschiedene Betriebsmodi und Umgebungsbedingungen simulieren.

Die Endkontrolle und Funktionstests sind nicht nur Qualitätssicherungsmassnahmen, sondern liefern auch wertvolle Daten zur kontinuierlichen Verbesserung des Fertigungsprozesses. Jeder entdeckte Fehler wird analysiert, um seine Ursache zu verstehen und zukünftige Vorkommen zu verhindern.

Mit dem Abschluss dieser umfassenden Testphase ist der Fertigungsprozess der Leiterplatte vollständig abgeschlossen. Das Resultat ist eine hochqualitative, zuverlässige elektronische Baugruppe, bereit für den Einbau in das Endprodukt oder den Versand an den Kunden.

Die moderne Leiterplattenfertigung ist ein beeindruckendes Zusammenspiel aus Präzisionstechnik, chemischen Prozessen und fortschrittlicher Automatisierung. Von der ersten Designphase bis zum finalen Funktionstest erfordert jeder Schritt höchste Genauigkeit und Kontrolle. Während die Grundprinzipien der Leiterplattenfertigung seit Jahrzehnten bestehen, treiben kontinuierliche Innovationen in Materialwissenschaften, Fertigungstechnologien und Qualitätskontrolle die Grenzen des Machbaren immer weiter. Diese Fortschritte ermöglichen die Entwicklung immer leistungsfähigerer, kleinerer und zuverlässigerer elektronischer Geräte, die unser tägliches Leben in vielfältiger Weise beeinflussen.